Real Time DMAS Beamforming

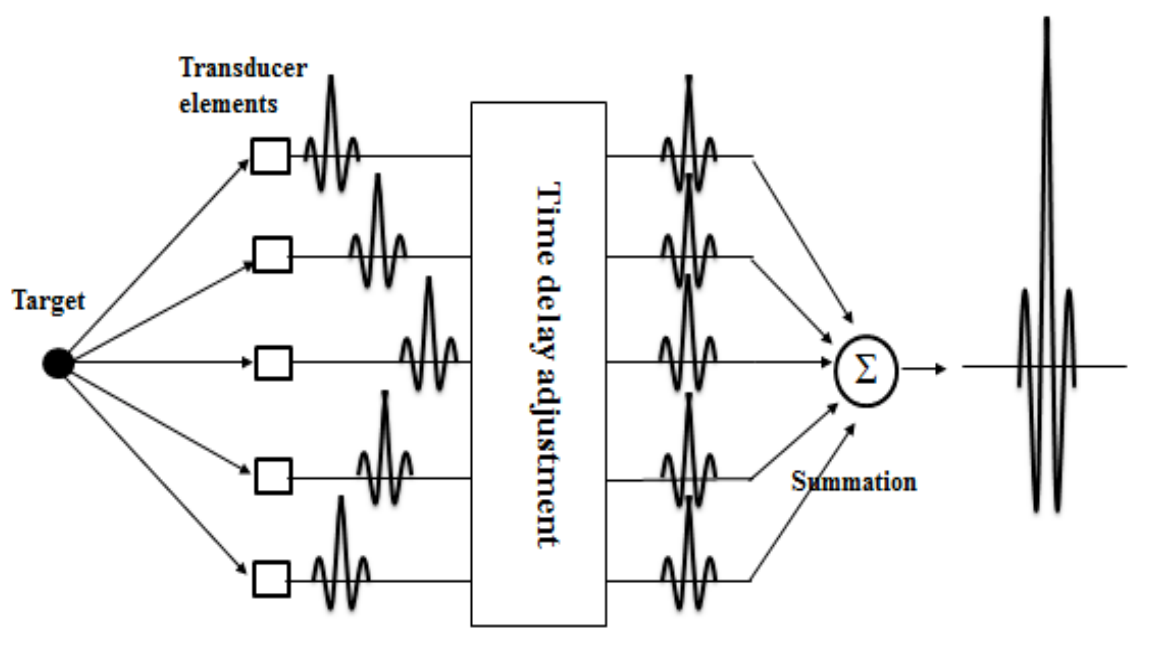

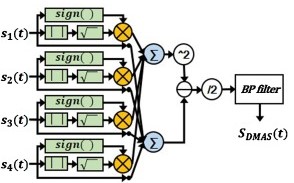

Oversimplifying, my contribution to this work was an algebraic rearrangement. False modesty aside, such rearrangement makes the real-time implementation of the Delay Multiply and Sum (DMAS) beamforming algorithm possible. The intuition came while I was a student attending the "Sensors and Transducers" course during my Master's. As a project for the class, I was implementing the classic Delay-and-Sum (DAS) beamforming algorithm on a Nvidia Jetson TK1 board. During a seminar, an invited researcher mentioned their novel DMAS algorithm for ultrasound medical imaging. Apparently, the algorithm gave better contrast and resolution, but its complexity limited its real-time implementation. Intrigued by it (and to please my professors during the final exam), I wondered how to integrate this new algorithm into my DAS GPU implementation.